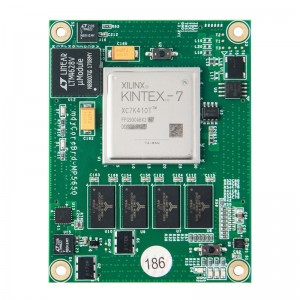

FPGA XILINX-K7 KINTEX7 XC7K325 410T Klas Endistriyèl

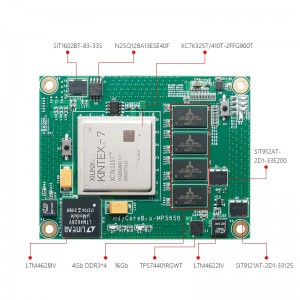

DDR3 SDRAMQ: 16GB DDR3, 4GB pa pyès, 16bit Data Bit Data Bid SPI Flash: Yon pyès 128MBITQSPIFLASH, ki ka itilize pou fichye konfigirasyon FPGA ak depo done itilizatè. Nivo koòdone FPGA Bank: reglabl 1.8V, 2.5V, 3.3V elektrik. Si ou bezwen ranplase nivo a, ou sèlman bezwen ranplase pozisyon korespondan pèl mayetik la pou reyalize ajisteman an. Alimantasyon kat debaz: seri ekipman pou pouvwa 5V-12V EEPROM; M24C02-WMN6TP baze sou aparèy bis I2C. Swivan metòd demaraj pwotokòl dezyèm liy kat debaz la: sipòte de mòd demaraj, ki se konektè Flash JTAG, QSPI. Pò pwolonje, 120pin, Panasonic AXK5A2137yg MP5700 plak anba koòdone SFP: 2 modil optik ka reyalize kominikasyon fib optik gwo vitès, jiska 6GB/s. Revèy plak anba: 1 revèy referans 200MHz konekte ak tablo debaz la. Pye tib revèy MRCC, 1 125MHz. Pye tib revèy GTX la. Plak anba koneksyon revèy la ak tablo debaz la se yon pò ekspansyon 40 pin: rezève yon pò ekstansyon 40-shot espasman estanda 2.54mm, ki itilize pou konekte pwòp modil konsepsyon kliyan an. Revèy tablo debaz Essence: gen plizyè sous revèy sou tablo a. Sa yo enkli revèy sistèm 200MHz la, revèy GTX 125MHz la, ak revèy EMCCLK 66MHz la. Pò JTAG: 10 pwen 2.54mm pò JTAG estanda, pou telechaje ak debogaj LED pou pwogram FPGA: yon total de 6 limyè wouj LED nan tablo debaz la, ki endike ekipman pou pouvwa kat tablo a, 4 limyè endikatè siyal ak pye tib FPGA IO konekte dirèkteman Kle: 4 kle. 4 kle. Sa yo se bouton reset FPGA, kle Program_b ak de kle itilizatè.

FPGA Xilinx-K7 Kintex7 XC7K325 410T a se yon modèl espesifik FPGA (Field-Programmable Gate Array) ki devlope pa Xilinx. Men kèk detay enpòtan sou FPGA sa a: Seri: Kintex-7: FPGA seri Kintex-7 Xilinx yo fèt pou aplikasyon ki gen gwo pèfòmans epi yo ofri yon bon balans ant pèfòmans, puisans ak pri. Aparèy: XC7K325: Sa a refere a aparèy espesifik ki nan seri Kintex-7 la. XC7K325 la se youn nan varyant ki disponib nan seri sa a, epi li ofri sèten espesifikasyon, tankou kapasite selil lojik, tranch DSP ak kantite I/O. Kapasite Lojik: XC7K325 la gen yon kapasite selil lojik 325,000. Selil lojik yo se blòk konstriksyon pwogramasyon nan yon FPGA ki ka configuré pou aplike sikui ak fonksyon dijital. Tranch DSP: Tranch DSP yo se resous pyès ki nan konpitè dedye nan yon FPGA ki optimize pou travay pwosesis siyal dijital. Kantite egzak tranch DSP nan XC7K325 la ka varye selon varyant espesifik la. Kantite Antre/Sòti: "410T" nan nimewo modèl la endike ke XC7K325 la gen yon total 410 broch Antre/Sòti itilizatè. Broch sa yo ka itilize pou konekte ak aparèy ekstèn oswa lòt sikui dijital. Lòt Karakteristik: FPGA XC7K325 la ka gen lòt karakteristik, tankou blòk memwa entegre (BRAM), transceiver gwo vitès pou kominikasyon done, ak divès opsyon konfigirasyon. Li enpòtan pou note ke FPGA tankou Xilinx-K7 Kintex7 XC7K325 la se aparèy pwogramasyon ki pèmèt ou aplike sikui dijital koutim ak fonksyonalite lè w pwograme selil lojik yo. Fleksibilite sa a fè yo apwopriye pou yon pakèt aplikasyon, tankou informatique pèfòmans wo, pwosesis siyal dijital, ak akselerasyon pyès ki nan konpitè.

Kategori pwodwi yo

-

Telefòn

-

Imèl

-

Whatsapp

-

Skype

-

Skype

-

Skype