Sèvis fabrikasyon elektwonik yon sèl kote, ede ou fasilman reyalize pwodwi elektwonik ou yo soti nan PCB ak PCBA

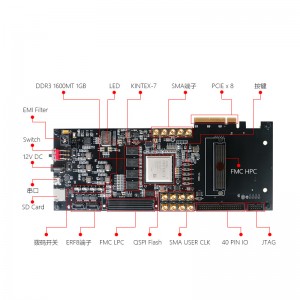

FPGA Xilinx K7 Kintex7 PCIe kominikasyon fib optik

- DDR3 SDRAM: 16GB DDR3 64bit bus, vitès done 1600Mbps

- QSPI Flash: Yon moso QSPIFLASH 128mbit, ki ka itilize pou dosye konfigirasyon FPGA ak depo done itilizatè.

- Entèfas PCLEX8: Entèfas estanda PCLEX8 la itilize pou kominike avèk kominikasyon PCIE kat manman òdinatè a. Li sipòte estanda PCI, Express 2.0. Vitès kominikasyon yon sèl kanal la ka rive jiska 5Gbps.

- Pò seri USB UART: Yon pò seri, konekte ak PC a atravè kab miniusb la pou fè kominikasyon seri.

- Kat Micro SD: Kat Microsd chita nèt, ou ka konekte kat Microsd estanda a

- Capteur tanperati: yon chip capteur tanperati LM75, ki ka kontwole tanperati anviwònman an ozalantou tablo devlopman an

- Pò ekstansyon FMC: yon FMC HPC ak yon FMCLPC, ki ka konpatib ak divès kat ekspansyon estanda

- Tèminal koneksyon gwo vitès ERF8: 2 pò ERF8, ki sipòte transmisyon siyal ultra gwo vitès. Ekstansyon 40pin: rezève yon ekstansyon jeneral koòdone IO ak 2.54mm40pin, O efikas gen 17 pè, sipòte 3.3V.

- Koneksyon periferik nivo a ak nivo 5V a ka konekte periferik periferik diferan interfaces 1O jeneral-bi.

- Tèminal SMA; 13 tèt SMA plake lò kalite siperyè, ki pratik pou itilizatè yo kolabore ak kat ekspansyon AD/DA FMC gwo vitès pou koleksyon ak pwosesis siyal.

- Jesyon Revèy: Sous plizyè revèy. Sa yo enkli sous revèy diferansyèl sistèm 200MHz SIT9102 la

- Kristal diferansyèl osilan: kristal 50MHz ak chip jesyon revèy pwogramasyon SI5338P: ekipe tou ak

- 66MHz EMCCLK. Ka adapte avèk presizyon ak diferan frekans revèy itilizasyon

- Pò JTAG: 10 pwen 2.54mm pò JTAG estanda, pou telechaje ak debogaj pwogram FPGA yo

- Chip siveyans vòltaj sub-reset: yon moso chip siveyans vòltaj ADM706R, ak bouton ki gen bouton an bay yon siyal reset mondyal pou sistèm nan.

- LED: 11 limyè LED, endike ekipman pou pouvwa kat tablo a, siyal config_done, FMC

- Siyal endikatè pouvwa, ak 4 LED itilizatè

- Kle ak switch: 6 kle ak 4 switch se bouton reset FPGA,

- Bouton Pwogram B ak 4 kle itilizatè yo konpoze. 4 switch doub kouto sèl

Ekri mesaj ou a isit la epi voye l ban nou

Kategori pwodwi yo

-

Telefòn

-

Imèl

-

Whatsapp

-

Skype

-

Skype

-

Skype